PADS Professional

Xpeditionのテクノロジを活用した総合型PCB設計ツール

PADS Professionalは、複数の設計ドメインにまたがる広範な作業をこなす独立系ハードウェアエンジニア向けに構築されました。Xpeditionのテクノロジを活用しており、ほかのソリューションでは対処することが困難な、極めて要求の厳しい複雑な設計にも対応します。

高い性能と使いやすさを両立し、価格もお手頃です。経験豊富なユーザには十分なキャパシティを、使用頻度の少ないユーザには直観的な使いやすさを提供します。短い時間で操作を習得し、すぐに実設計業務に取りかかれます。

高度なFPGAデバイスを搭載したPCBベースのシステムの設計、検証、製造に対応した包括的な設計フローです。

最新情報は、メーカーのサイトをご参照願います。

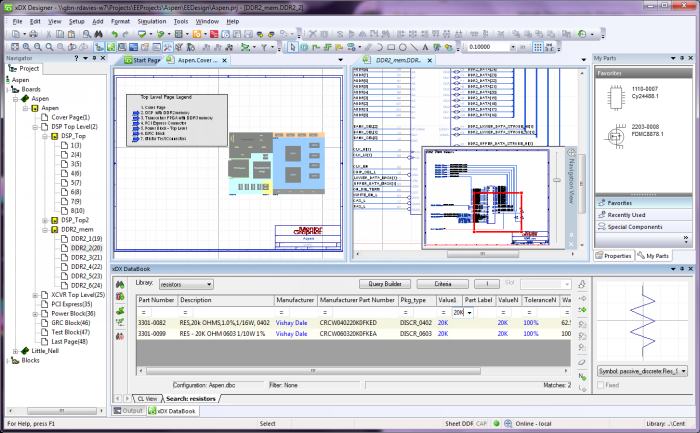

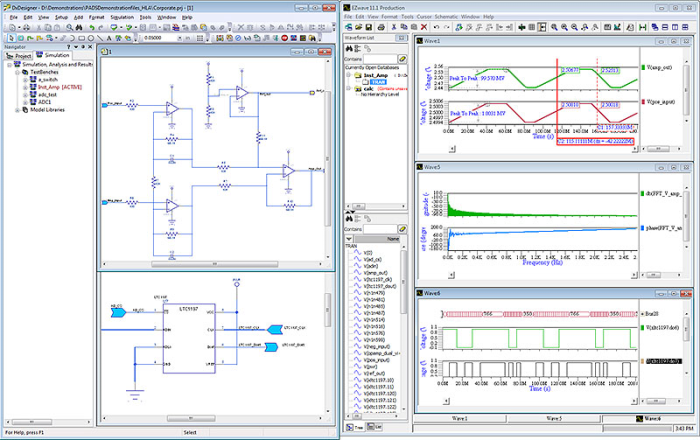

回路設計

回路図設計の入力と再利用のための包括的なソリューション

PADSの回路図入力環境は、回路図の入力/定義をシンプルかつ高速に実現する完全な回路設計ソリューションを提供します。デスクトップ上に一体化したことで、エンジニアは主要な各種設計タスクを単一の環境で進められます。回路設計、シミュレーション、部品選択、ライブラリ管理、シグナルインテグリティのプランニングに必要なあらゆる機能が備わっています。また、直感的なプロジェクトおよび設計ナビゲーション、階層構造の完全サポート、設計ルールおよび属性を管理する高度なツールによって、各PCB設計の目標達成を支援します。

設計資産の管理と生産性向上

部品の管理、回路図とレイアウト間のフォワードアノテーションおよびバックアノテーション、シグナルインテグリティ解析と直結した環境など、回路図構築を成功させる各種機能によって効率性と生産性を強化します。

設計制約は、必要に応じて回路図設計の早い段階からいつでも設定および検証することができます。また、ライブラリコンテンツへの迅速なアクセスが可能なため、新しいシンボルの検索、配置、検証が簡単です。さらに、ハイレベルな自動化機能に加えて、グラフィックを用いた高度な拡張ツールチップが提供されていることで、使用頻度の高いユーザに限らず、たまにしか使わないユーザでも、PADSを簡単に効率良く使うことができます。

設計の再利用とバリアント設計もサポートされているため、製品のTime-to-Marketを短縮しながら製品品質を向上し、生産コストを削減することが可能です。

統合とスケーラビリティ

直感的な操作と高いスケーラビリティを提供するPADSは、生産性の高い設計環境を創出し、設計サイクルタイムを短縮します。高度に統合された機能によって、設計入力から部品情報管理、設計バリアント管理、解析から検証にまで対応しています。

・一度入力した設計を再利用して開発を高速化

・階層構造の再利用可能な設計ブロックを活用して設計時間を短縮

・部品データベースに簡単に接続して手早く部品検索

・回路図とレイアウト間で設計を検証して更新

・クロスプローブ、バックアノテーション ほか

階層構造の設計定義環境

複数のシート、制約条件、シミュレーション機能とともに、設計意図を1箇所で管理します。

部品情報管理機能との統合によるインテリジェントな部品選択

標準的な各種部品データベースから、部品を迅速に検索し、選択することが可能です。

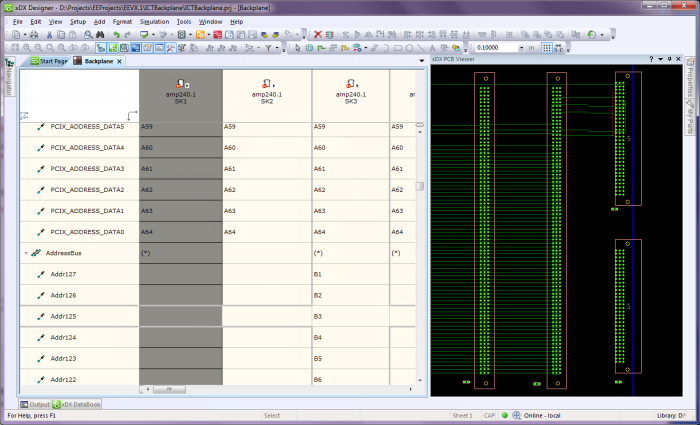

FPGAやコネクタ、バックプレーンといった多ピンデバイスの

テーブルベース設計向けのインターコネクトエディタ(ICE機能)

複数シートにまたがるシンボルに悩まされることなく、多ピンデバイスの接続を迅速に定義します。

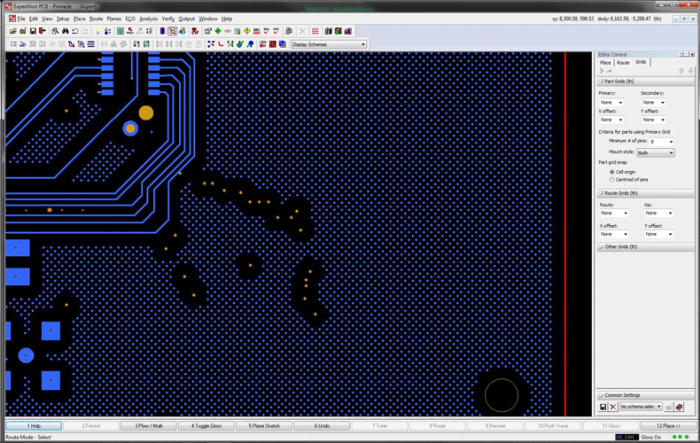

レイアウト

業界をリードするテクノロジを用いて最高難度の設計を構築

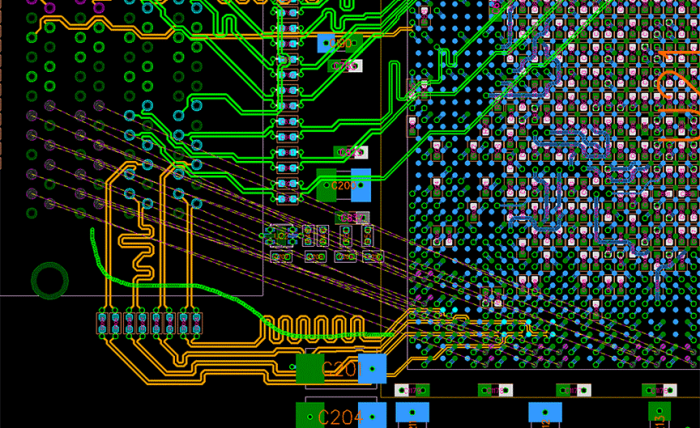

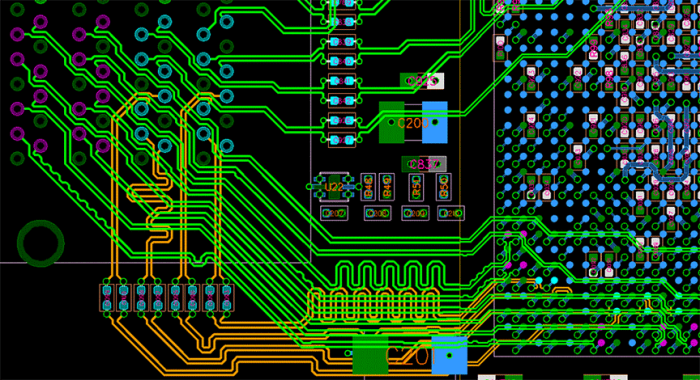

使いやすさと高度な自動化機能を組み合わせたPADS Professionalのレイアウトツールは、極めて複雑なPCB設計作業に対して抜群のコントロール力を発揮します。

スケッチ配線機能(Sketch Router)は、対話型編集時に自動配線の利点とユーザ制御力を組み合わせることで、非常に優れたパフォーマンスと高品質の仕上がりを実現します。

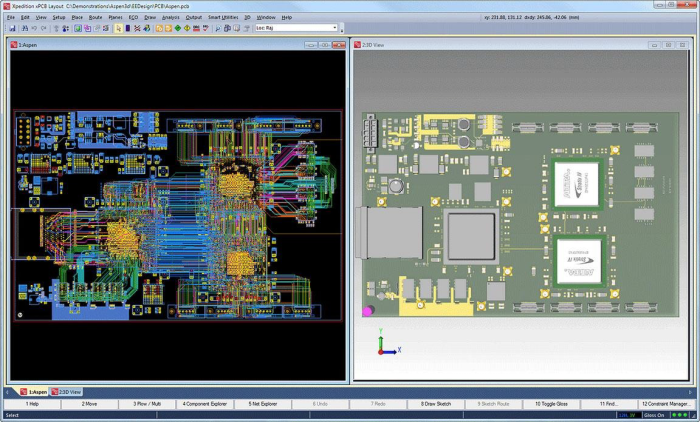

2Dと3Dの設計環境が完全に統合されており、PCBレイアウト段階からエレメカ設計最適化の課題に対処することができ、工程終盤でのコストのかかる設計やり直しを回避します。部品のプランニングと配置は、写真精度の3D部品、基板ストラクチャ、筐体を使用して2D環境または3D環境で仕上げることができます。

■機能

・ 3DレイアウトとMCADコラボレーション

・ 自動化された配置プランニングと管理

・ 自動化を取り入れた対話型スケッチ配線

・ RF/アナログ/デジタル/組込み設計の協調設計

・ 制約ドリブンのハイスピードネット配線とチューニング

・ 製造性を考慮した設計最適化

2D編集環境に3D編集環境を統合

部品の選択、プランニング、配置機能の操作はこれまでと同じです。新たに操作を習得する必要がないので、設計スケジュールに影響しません。

配置プランニングと管理

エンジニアの設計意図を素早く可視化して実践し、最適な部品配置を実現します。

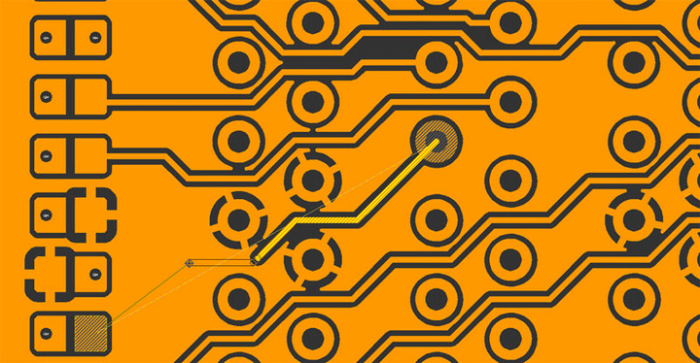

半自動の対話型スケッチ配線のテクノロジ

Sketch Router、Hug Router、Real Trace Routing、Dynamove等一連の自動配線ツールを1つに統合しました。これらの機能は高い品質と抜群の性能を備え、直感的なユーザ制御力を取り入れた自動配線を実現します。

半自動の対話型スケッチ配線のテクノロジ

DRCエラー修正の工数を減らし、設計プロセス全体を通じて設計が常に正しい状態になっていることを確実にすることで、全体的な効率性と品質を向上します。その結果、初回から正しい設計が得られることになります。

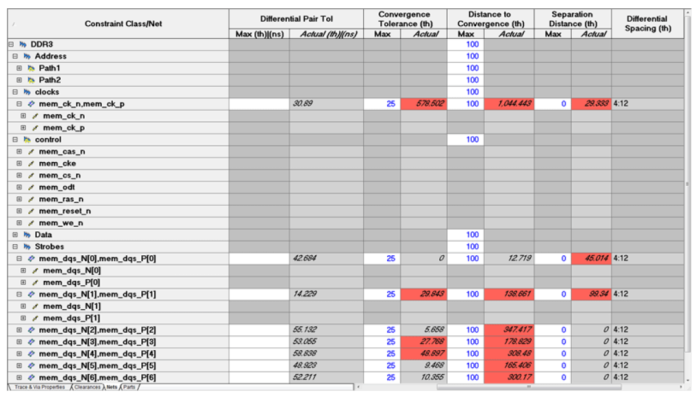

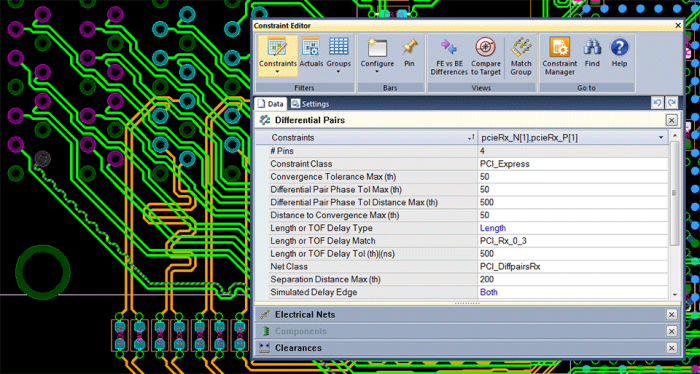

最も重要な設計課題に対処

差動ペア配線、ネットのチューニング、製造の最適化、フレックス回路、埋め込み受動および能動部品、RF回路、マイクロビアテクノロジといった複雑な設計課題に対処するために必要なあらゆるツールを提供します。

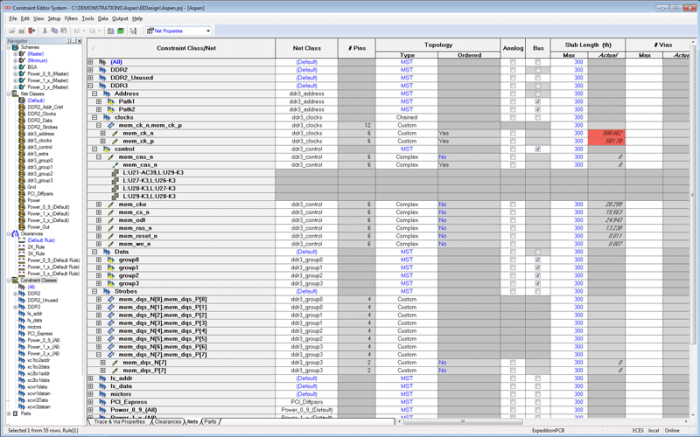

制約条件管理

制約条件管理機能を統合して、Correct-by-Construction(構築することで正しい結果が得られる)設計を実現

PADS Professionalを使用すると、高密度化と複雑化の進むPCB設計であっても設計ルールに厳密に準拠させることが可能です。設計ルールのドキュメント化、変換、解釈を手作業で行うと、製品開発サイクルの長期化やコスト増加を招くこともめずらしくありません。

しかし、Xpeditionのテクノロジを利用したPADS Professionalは、制約ドリブンの設計メソドロジを完全に統合しているため、設計ルールの伝達を自動化し、不要なPCBプロトタイプ作成やリスピンを回避することで設計コストの削減とTime-to-Marketの短縮を実現します。

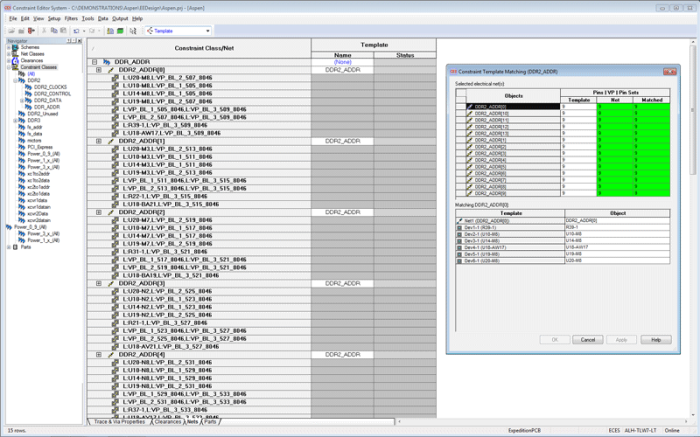

複雑なルールを複数のネットに適用できる制約テンプレートを使って、共通環境でコンカレントに制約を

編集し、クロスプローブさせることで、レイアウトを設計意図に照らして直接検証することが可能です。スプレッドシートベースの制約編集環境では、フロー内の回路図入力ツールと物理設計ツール間で双方向にクロスプローブ、ハイライト、選択しながら、制約条件を直接検証します。

・ 一度入力した制約条件は、設計フロー全体に適用可能

・ 階層構造のルールを用いて、クラス、ネット、グループ、ピンペアなどを正確に制御

・ ハイスピード設計のルールを用いて配線が性能要件を確実に満たすことを確認

・ 制約条件をネスト化して、設計フロー内でより効率的に配線を制御

・ 等長、差動ペア、最大/最小長などハイスピード設計のルールを定義

プロセス全体を通じて設計意図を維持

設計入力環境とレイアウト環境間で双方向にクロスプローブ、ハイライト、選択し、設計意図を正確に効率よく取り込み、確実に適用します。

電気的および物理的制約条件を単一の環境で定義して検証

複数のデータベースを構築する必要はありません。

簡単な制約条件の入力が設計プロセスを高速化

設計内および設計間で制約条件が再利用できるだけでなく、制約条件の同時入力もサポートしています。

コンテキストに応じて制約条件を入力

回路図エディタからもPCBレイアウトエディタからも簡単に制約条件の更新が可能です。

解析

高性能設計に対応したPCBシミュレーションソリューション

PADS Professionalは、HyperLynxのテクノロジに基づいてPCB設計を解析/検証できる包括的なソフトウェアスイートとして、基板設計フローのあらゆる段階でPCBハードウェアエンジニアのニーズを満たします。使い勝手に優れたHyperLynxは、クリティカルな要件を効率的に解析、解決、検証することで、コストのかかるリスピンを減らします。その結果、優れたイノベーションの創出、Time-to-Marketの短縮、コストの削減を実現します。

アナログシミュレーション

SPICE、VHDL、Verilogの業界標準言語を使用してPCB全体の機能をシミュレーションできます。

内蔵の波形表示機能や解析エンジンによって、マルチカーソルと対話的イベント検索機能を使った

遷移点間測定、特殊なダイアグラムやチャートの作成、波形ポストプロセスが可能です。

1つの回路図でシミュレーションとPCB設計に対応しているため、設計転写エラーもなくなり、

製品のTime-to-Marketが短縮します。

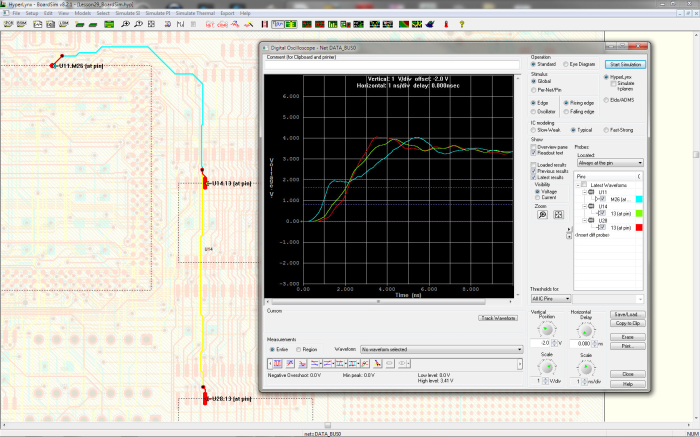

シグナルインテグリティ

クロストークを含めたシグナルインテグリティに関する問題を設計早期から解析することで、コストのかかるリスピンを減らします。PADS Professionalは、回路図設計から最終レイアウト検証に至るまで設計フロー全体に緊密に統合されています。

簡単で迅速、正確に生成されるシグナルインテグリティ解析結果に基づいて、ルールの検討、定義、検証を効率化することで、設計意図を確実に反映させます。トレースインピーダンス、カップリング、周波数依存の損失といった伝送線路の正確なモデリングにも対応しています。

また、終端処理ウィザードを使うと、ディスクリート、トレース形状、トレース長、ドライバ設定といったさまざまな値をスイープさせながら、最適な終端処理法を求めることができます。

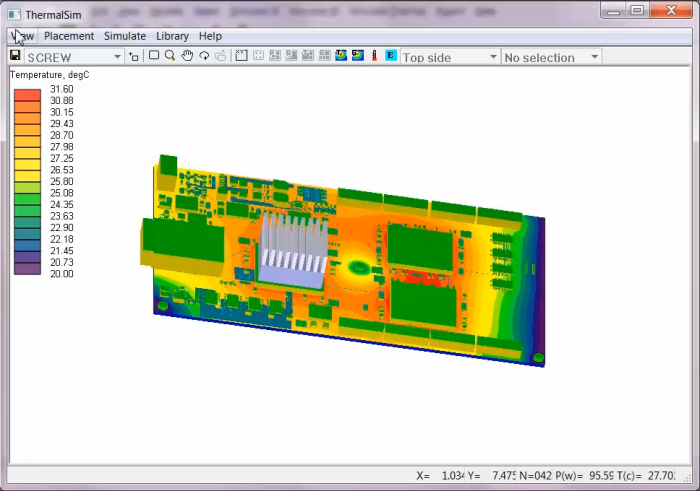

熱解析

PCB上の部品配置と配線を素早く正確に3Dモデリングし、熱の影響をシミュレーションします。部品配置、積層設計、物理的な冷却技法について効果的にwhat-if(仮定条件)解析を行うことで、部品やPCBのホットスポットを迅速かつ効率的に特定します。対流、伝導、放射など主要な熱伝導メカニズムをすべて解析できます。

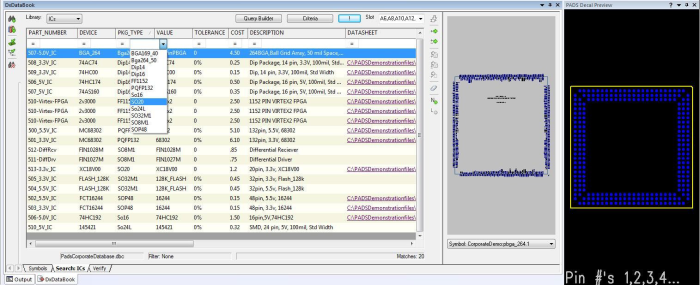

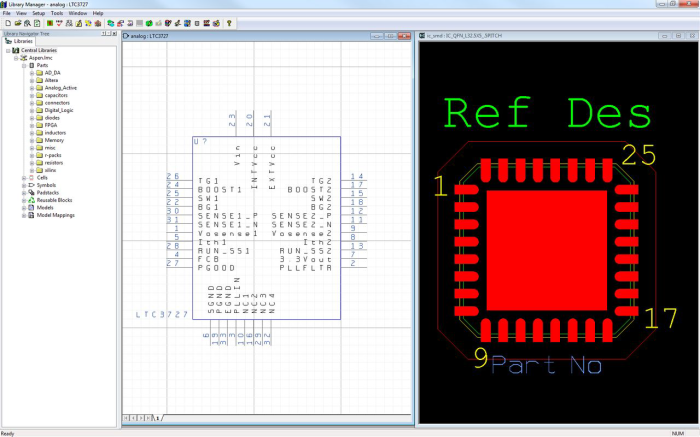

プロジェクトデータ管理

部品を構築および管理し、アーカイブ管理を自動化

設計プロセス全体にわたって統合型ライブラリ管理機能を利用できるため、部品の構築と管理や自動アーカイブ管理が可能になり、手作業のバックアップ作成にかかる時間と間接費を削減します。

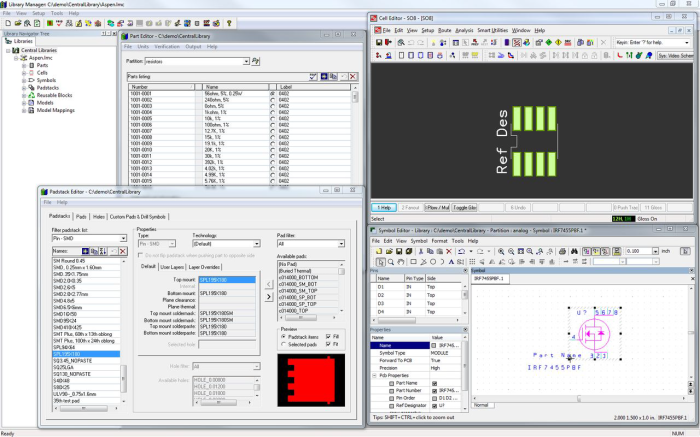

■ライブラリ作成と編集

共有ライブラリでは、複雑なPCBシステムに求められる論理的および物理的部品データのあらゆる要素を管理します。シンボル(論理的ビュー)、セル(物理的なフットプリント情報)、パッドスタック、論理対物理のピンマッピング(部品データ)などを集約し、中央で一元的に部品管理を行います。

ナビゲータツリーによって部品の関係を視覚的に表示

PCB部品データの論理対物理マッピングのあらゆる要素をこのナビゲータツリーから一括して作成できます。

シンボル、セル、パッドスタック、部品の各エディタを統合

一貫性チェックと検証の機能を内蔵しました。

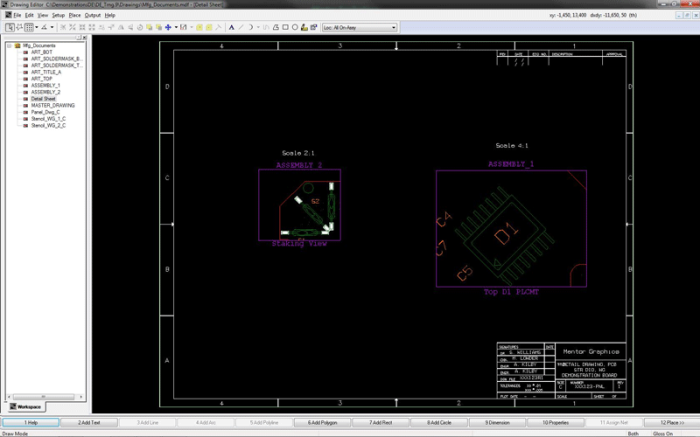

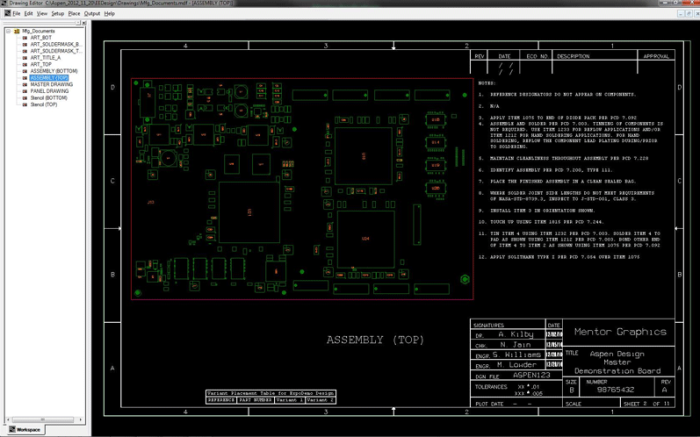

製造準備

製造工程に渡す前に、設計の製造容易性を検証

PADS Professionalに統合された製造準備環境は、製品品質を最適化し、サイクルタイムとコストを削減します。設計者は、基板レベルあるいはパネルレベルのどちらでもドキュメンテーションを作成し、製造にすぐ使えるデータを出力することが可能です。レイアウト環境とも緊密に統合されているため、レイアウト中に生じた変更は製造用図面にも反映されます。

また、PADS ProfessionalはValor NPIとも緊密に統合されており、コンカレントにDFM(製造を考慮した設計)を実行し、ODB++フォーマットを使ってすべての製造データに抜けがなく同期が取れていること、設計意図が保たれていることを確認しながら、最適化した設計を製造へ引き渡すことができます。そのほか、Gerber、NCドリル、実装データなどのCAMフォーマットやレポートにも対応しています。

柔軟かつ詳細に表示

PCB設計あるいはパネル設計の特定部位を詳細表示または拡大表示できます。

銅箔バランス調整

PCB設計でもパネル設計でもバランスのとれた設計を実現します。

レイアウトとの統合

最終レイアウト編集と並行して製造準備を進められます。

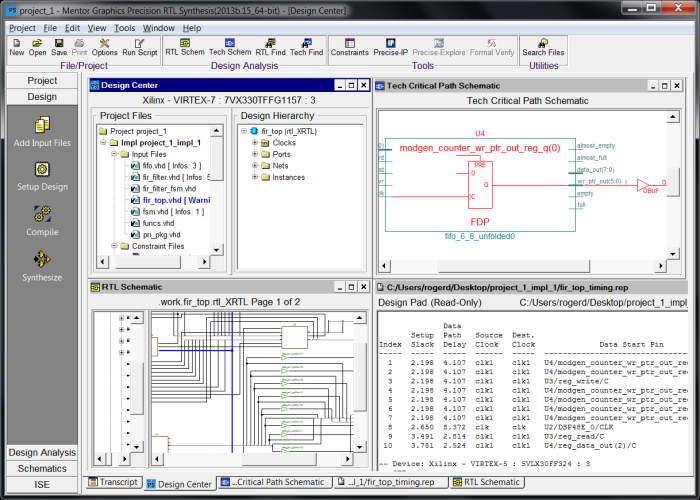

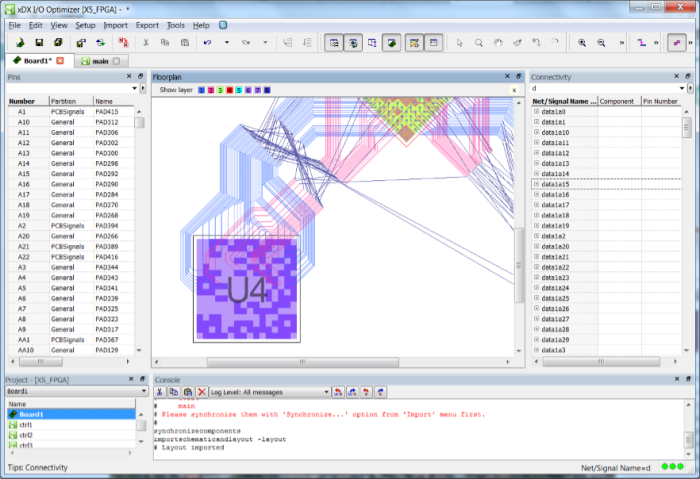

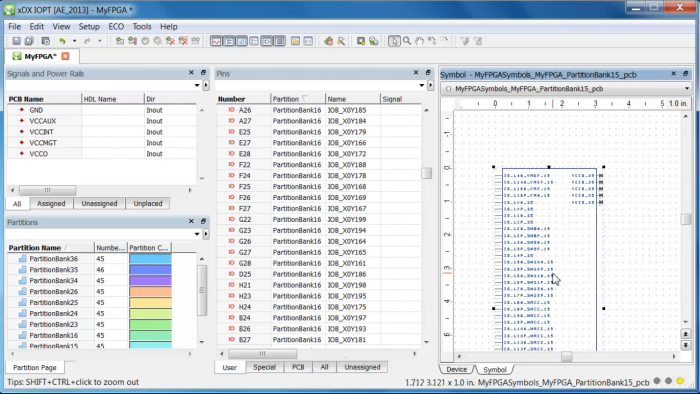

FPGA-PCB協調設計(オプション)

合成とI/O最適化の機能を統合したFPGA/PCBの協調設計

今日のFPGAはASICやSoCと同様に複雑化しつつあることから、FPGAを実装するより高度なフローが検討されるようになってきました。FPGAベンダに依存しない統合型設計環境の一環として提供される高度な合成テクノロジを使用することによって、各FPGAデバイスに特化したアーキテクチャ特性を最大限に生かした最適化を行い、個別の設計要件を満たすことができます。

PADS Professionalで提供されるFPGA I/O最適化ツールは、使いやすいさまざまな機能がそろっており、

回路図/PCBエンジニアがFPGAをPCB上に統合する作業を包括的に支援します。また、高精度で高速なコンカレントな設計プロセスも実現します。Correct-by-Construction(構築することで正しい結果が得られる)手法を通じて、PCB設計工程でFPGAのI/Oピンを再割り当てし、レイアウトに基づいた最適化をPCB工程の中でできるので、PCBシステムのTime-to-Marketと製造コストを劇的に削減させます。

変化の激しい今日の設計環境において、これは非常に重要です。

・ シリアルな設計プロセスをコンカレントな設計プロセスに変えることで、

トータルの製品設計サイクルタイムを短縮

・ PCB信号層をなくすことでPCB製造コストを節約

・ 誤ったFPGAシンボルが配置されるのを防止し、PCBのリスピンを削減

・ 高速なパフォーマンス最適化機能を搭載

・ PCB回路図用にFPGAシンボルを作成/管理するコストを削減

PCBのコンテキストに応じてFPGAのI/Oを最適化

FPGA設計を、レイアウト工程で使用するPCB回路図に素早く変換します。

PCBシンボルと回路図を迅速かつ簡単に作成

FPGA設計を、レイアウト工程で使用するPCB回路図に素早く変換します。

I/Oの精度を向上

PCBの層数やビア数を削減し、トレースの長さを短縮します。

ベンダに依存しない環境で高度な合成テクノロジを実現

各FPGAデバイスのアーキテクチャを個別に最適化します。