HyperLynx SI

設計の早い段階でシグナルインテグリティに関する問題を解析

コストのかかる手戻りを削減

HyperLynx SIは、PCBシステム設計におけるシグナルインテグリティの解析結果を迅速に、簡単に、そして正確に生成するため、ルール探索、定義、検証を効率的に管理し、確実に設計の目的を達成できるようにします。HyperLynx SIには、回路設計から最終レイアウト検証に至るまですべての機能が統合されています。また、オーバーシュート/アンダーシュート、リンギング、クロストーク、タイミング問題など、ハイスピード設計が抱える典型的な問題にも迅速かつ正確に対処します。

包括的なSerDes設計のサポート

FastEyeダイアグラム解析、Sパラメータシミュレーション、BER予測を含みます。

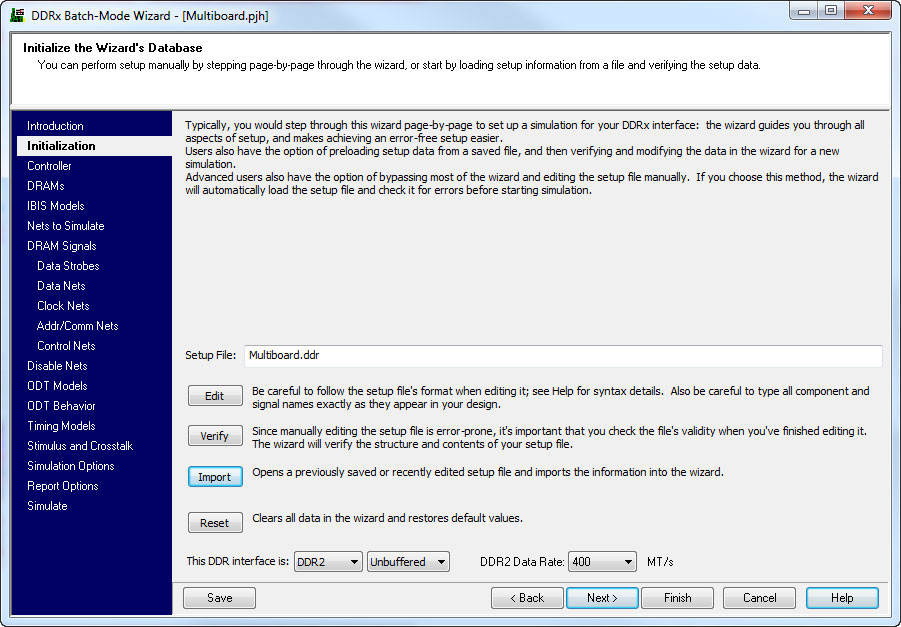

DDRxウィザード

セットアップ、またタイミングを含むDDRプロトコルメモリシステムの検証を容易にします。

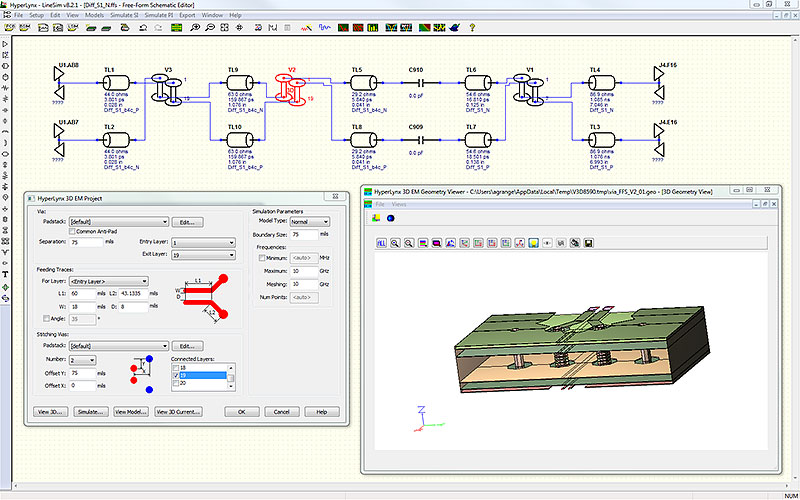

フルウェーブ3D EMフィールドソルバを統合

HyperLynx SIは、差動ビアを含む詳細な構造解析を容易にします。

技術仕様

- 業界で定評ある使いやすさ: 短時間での結果生成

- トレースのインピーダンス、カップリング、周波数依存の損失を正確にモデリング

- ディスクリート、トレース形状、トレース長、ドライバ設定に対してさまざまな値をスイープ

- ターミネータ・ウィザードにより最適な終端抵抗を提案

- DDRxウィザードにより、タイミングを含むDDR、DDR2、DDR3メモリ・システムの完全な検証が可能

- シリアル・インタフェースBER(Bit Error Rates)、ワーストケース・ビット・シーケンス、アイ・ダイアグラムを数週間ではなく数時間で正確に予測

- 高度な探索型のビア・モデリング

- フルウェーブ3D EMフィールドソルバを統合

- EMCエラーの可能性を早期に予見

- HSPICE、Eldo、IBIS-AMI、AMS、Sパラメータ、IBISモデルを容易にインスタンス化

- プリレイアウトモードによって、設計の探索、回路図検証、制約の定義を実施

- ポストレイアウトモードによって、完全バッチ処理による設計の検証を実施

- 回路図、制約、レイアウト環境を含むXpedition Enterpriseフローと統合

- EBDモデル、コネクタモデルを含む強力で使いやすいマルチボード解析

SerDes設計

HyperLynx SIでSerDes設計の課題を迅速に解決

HyperLynx SIは、SerDes設計を最適化するための高度なツールを備えています。設計とモデリングのための独自の機能により、ジッタ、オーバーシュート、アンダーシュート、リンギング、クロストーク、損失、反射など一般的な高速シリアル設計上の問題を回避しながら、シリアル・チャネルの性能と信頼性を最大限に引き出します。

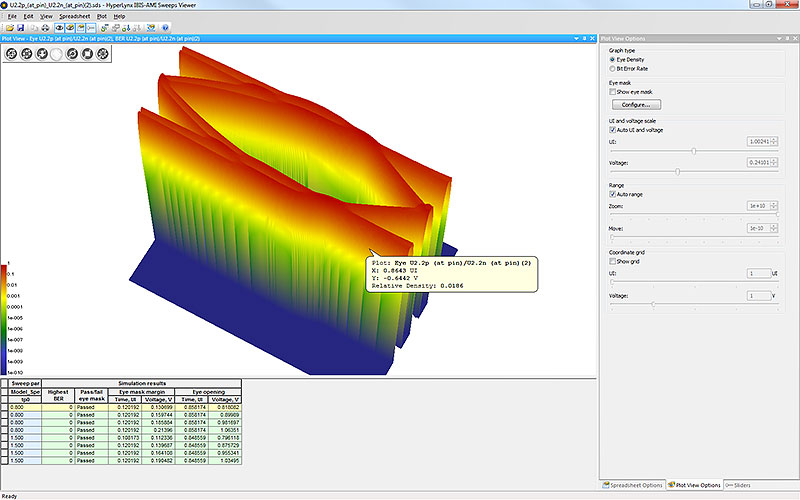

- FastEye線形チャネルの解析

- BER(ビット・エラー・レート)情報の統計的な後処理

- プリエンファシスのIBIS-AMI特性評価、イコライゼーション、クロックリカバリー

HyperLynx SIは、エレクトロニクス業界のあらゆる分野で規定されている高速シリアル・チャネル標準規格に対応した設計とその検証のためのツールです。

- コンシューマ向けオーディオ/ビデオ、コンピュータ関連、通信、携帯電話に使用されるすべての汎用マルチギガビットSerDes設計標準に対応

- レイアウト配線前の高速チャネル設計を調整するための高速かつ効率的な仮想プロトタイピング環境を提供

- プリエンファシス、イコライゼーション、複雑なクロックリカバリー付きの最先端I/Oアーキテクチャをモデリング

解析とシミュレーション

部品や製造上の公差に十分なマージンを確保しつつ、性能を最大化できる設計を実現するため、SerDes設計の解析とシミュレーションはモデル精度とシミュレーション速度の両方を兼ね備えている必要があります。

- SerDes設計に信頼性、スピード、精度をもたらすSパラメータ・シミュレーション

- HyperLynx SIにより精巧なポール・フィッティング・アルゴリズムによる周波数ベースのシミュレーションを実行できます。周波数情報が限定されたシミュレーション・モデルも使用できます。

- 効率的な単一カーネル・シミュレーションのためのQuesta ADMS

- HyperLynx SIは効率的で、回路レベルとシステム・レベルの同時シミュレーションが可能な唯一のSerDes設計ツールです。ほかの設計ツールで発生しやすいプロセス間通信オーバーヘッドを回避します。

- チャネル・シミュレーション極限加速のためのFastEye解析

- HyperLynx SI FastEyeスイートには、毎分100万ビット以上の伝搬をシミュレーションできるマルチギガビット・ドライバ/レシーバの線形モデルが採用されています。これまで数日を要していた1e-15 BER性能の検証が数時間で完了します。

- 主要CADベンダ各社のソフトウェアと互換性を持つプリ/ポスト・レイアウト解析

- HyperLynx SIのポスト・レイアウト・チャネル解析では、レイアウト上で修正した部分がSerDes設計性能に著しく影響を与えないことを確認できます。

DDRx設計の検証

HyperLynx SIのDDRxウィザードを使用すると、わずか数回のクリックでDDR2/3/4とLPDDR2/3/4の設計の課題を特定し、その課題に対応することができます。

HyperLynx SIにはDDRxベースの設計を解析する強力な機能が備わっており、設計/デバッグサイクルの大幅な短縮を実現します。符号間干渉(ISI)やクロストークといったボードレベルの影響を考慮して、セットアップ/ホールドタイム、オーバーシュート/アンダーシュート、単調性などの信号品質パラメータを特性評価し、JEDEC標準または顧客要件に準拠した設計であるかを検証します。

- DDRはDDR4まで、LPDDRはLPDDR4までをサポート

- DDR/LPDDRのすべてのランクにおいてチャネル全体、アドレス、コマンド、データバスのシミュレーションが可能

- シミュレーション結果の波形を自動的に解析し、重要部分をハイライト

- JEDEC準拠のAC/DCしきい値にIBISモデルを置き換え

DDRx設計入力

高速並列信号チャネルの標準規格であるDDRxは、メモリの並列バスアーキテクチャとして電子業界で広く採用されています。HyperLynxは、DDRx標準に準拠した設計と検証を可能にするツールです。付属のDDRxウィザードを使用すれば、並列チャネルが多数にのぼる場合であっても、シグナルインテグリティの細かな要件に適合しているかを自動的に検証できるので、高難度の検証課題の解決に役立ちます。

- コンシューマ向けのモバイル機器に使用されるLPDDRベース(LPDDR4を含む)の設計から、業務用ハイエンドサーバに用いられるSDRAMのDDR4にいたる標準的なすべてのDDRx設計標準に対応

- プリレイアウト解析によるトポロジの最適化と、ポストレイアウトの単一/マルチボードシステム解析の両方をサポート

- ケイデンス・デザイン・システムズAllegroをはじめとする主要な基板レイアウトツールからデータを容易に取り込み、解析可能

DDRxの解析とシミュレーション

DDRxバスを検証する際はタイミングと電圧値に基づき解析する必要がありますが、DDRxバス全体を手作業で解析するのは時間がかかり、現実的とは言えません。HyperLynxであれば、シミュレーションを短い時間でセットアップできることに加え、細かな解析データも入手可能なため、有益な情報をもとに設計判断を下すことができます。

- 波形形状に基づくディレーティングなど、JEDECの検証要件の自動取り込み

- コントローラの検証時など必要に応じてパラメータをカスタマイズ可能

- 「what-if」シナリオを網羅するスイープ試験/解析

- コントローラの読み出し/書き込み回数の平滑/較正機能

- 実際の電源ソースの影響を考慮(IBIS 5.0準拠のモデルを使用)